Innovative HIL Testbed Validates the Software Embedded in Socomec Uninterruptible Power Supply Systems

“Thanks to NI and OPAL-RT, we now have a real-time, high-performance hardware and software HIL validation solution to improve the quality of our products and reduce development time.”

– Thierry Rohmer, SOCOMEC SA

The Challenge:

We needed to build a hardware-in-the-loop (HIL) simulator for our electric power converters to validate complete functionality with strict real-time constraints and to test the robustness of our products under a broad range of use cases and non-ideal conditions.

The Solution:

We used NI hardware including PXI Express and FPGA boards that support the OPAL-RT eHSx64 solver. We also used NI software, including LabVIEW for model simulation and I/O management, VeriStand for real-time test execution, and TestStand for high-level test automation.

The Socomec Group is present on five continents through wholly owned subsidiary companies or distributors. Socomec is the leader in many endeavors dedicated to electrical equipment in the service sector and industrial applications, including power cut-off and protection systems (fuses, breakers, switches), energy efficiency (power meters, electrical sensors), power converters (uninterruptable power supplies), and service (product maintenance, training and advising customers).

Details of the Application

For our validation requirements, we sought a modular, turnkey solution with a history of proven success. We obtained proposals from various suppliers of hardware-in-the-loop (HIL) simulation systems. We chose the NI and OPAL-RT combination as their joint submission best met our requirements, including the need to:

- Simulate our converters operating with a chopping frequency exceeding 10 kHz (therefore a model that works beyond 200 kHz)

- Support over 150 simulation variables with more than 50 semiconductors, 36 PWM command inputs, and 30 real-time analog signals from the solver

- Avoid long compilation steps each time we modify the converter layout

- Have a single solution for simulating converters and the environment, ideally with a single interface

- Use market-standard products or languages

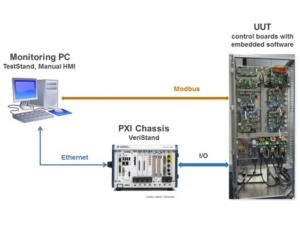

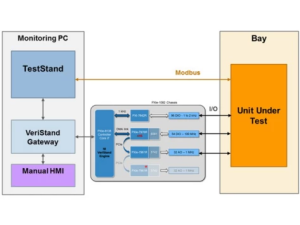

To meet these requirements, NI proposed a hardware and software solution that included implementing the OPAL-RT eHSx64 solver on a FlexRIO FPGA module, a customizable front end for PXI modules. This lets us change our digital models for power electronics on the fly. We use LabVIEW to simulate environment models and acquire and generate signals while VeriStand coordinates these aspects in real time.

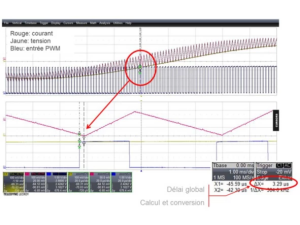

The testbed comprises a set of electronic cards under test that are slightly modified to make them compatible with the electrical signals entering or leaving the instrumentation rack. Every element is dedicated to a specific task. The controller runs models developed with LabVIEW for signals with lower real-time constraints like batteries or electric motors (< 5 kHz). The solver simulates the power converters and related filters (< 1 MHz), so it runs with a high degree of determinism thanks to the use of FPGAs.

The testbed comprises a set of electronic cards under test that are slightly modified to make them compatible with the electrical signals entering or leaving the instrumentation rack. Every element is dedicated to a specific task. The controller runs models developed with LabVIEW for signals with lower real-time constraints like batteries or electric motors (< 5 kHz). The solver simulates the power converters and related filters (< 1 MHz), so it runs with a high degree of determinism thanks to the use of FPGAs.

A Project Developed in Partnership With MESULOG

Once the entire team had taken the VeriStand and OPAL-RT training courses, the system became operational in less than a week. The systems engineers and R&D departments at NI and OPAL-RT deserve thanks for their high level of involvement. MESULOG, an NI Partner, also supported us throughout the project. We collaborated closely to perfect the manual HMI with a total investment of three man-months. Tests quickly highlighted possible improvements to our products, which was our goal, and further validated the technological choices made for this ambitious project.

Our next goal was to automate tests, so the team trained to use TestStand. While MESULOG worked on the software architecture and the production of business-oriented TestStand building blocks, we wrote specific test sequences communicating not only with the real-time test system, but also with the unit under test. In parallel with our development work, NI and OPAL-RT modified the solver to better meet our needs during the first months of development.

Our next goal was to automate tests, so the team trained to use TestStand. While MESULOG worked on the software architecture and the production of business-oriented TestStand building blocks, we wrote specific test sequences communicating not only with the real-time test system, but also with the unit under test. In parallel with our development work, NI and OPAL-RT modified the solver to better meet our needs during the first months of development.

System Advantages

We now have a well-integrated system in the highly flexible VeriStand testing environment for both high-speed FPGA solver and traditional CPU-based simulation models. The solution offers ease of development, greater control, and system stability. We no longer need to create an average converter model, but instead can count on the calculation power of the FPGAs, which considerably reduces the effort needed to implement the simulation model. We can change a layout and see the results of the changes made in less than a minute. This is priceless as the speed of iteration translates directly into shorter time to market for our products. If we find errors in the embedded control code, we can quickly isolate and correct them early in the design process.

To test robustness, HIL is the only way we can reliably validate the equipment under environmental conditions, including extreme temperatures and degraded power supply voltage/frequency conditions. The physical test resources available to us until now would never have allowed us to apply all the imaginable test cases that may be observed in countries far away. With this HIL testbed, developers gain access to a risk-free test platform. They can test functions and, when necessary, replay sequences that cause the embedded software to fail, all in a short amount of time.

Conclusion

We are achieving the goals we set for this investment and see encouraging results. We can deliver better quality products thanks to non-regression and robustness tests. We have reduced development and validation times. As the test system is highly flexible and easy to use, we foresee using it to validate new converter topologies before we even make the prototypes. Once most of the uninterruptible power supply tests have been written, we will look to test many units in parallel, which at a minimum will double the number of tests being run.

Author Information:

Thierry Rohmer

SOCOMEC SA